# CENTRO UNIVERSITÁRIO EURÍPIDES DE MARÍLIA FUNDAÇÃO DE ENSINO "EURÍPIDES SOARES DA ROCHA" BACHARELADO EM CIÊNCIA DA COMPUTAÇÃO

# LABORATÓRIO REMOTO PARA PROTOTIPAÇÃO DE CIRCUITOS DIGITAIS UTILIZANDO KITS DE DESENVOLVIMENTO FPGAS XILINX

**CRISTIANO VICENTE**

## CENTRO UNIVERSITÁRIO EURÍPIDES DE MARÍLIA FUNDAÇÃO DE ENSINO "EURÍPIDES SOARES DA ROCHA" BACHARELADO EM CIÊNCIA DA COMPUTAÇÃO

# LABORATÓRIO REMOTO PARA PROTOTIPAÇÃO DE CIRCUITOS DIGITAIS UTILIZANDO KITS DE DESENVOLVIMENTO FPGAS XILINX

Trabalho de Curso apresentado ao Curso de Bacharelado em Ciência da Computação da Fundação de Ensino "Eurípides Soares da Rocha", mantenedora do Centro Universitário Eurípides de Marília - UNIVEM, como requisito parcial para obtenção do grau de Bacharel em Ciência da Computação.

Orientador:

Prof. Dr. Fábio Dacêncio Pereira

# CENTRO UNIVERSITÁRIO EURÍPIDES DE MARÍLIA - UNIVEM MANTIDO PELA FUNDAÇÃO DE ENSINO "EURÍPIDES SOARES DA ROCHA"

#### BACHARELADO EM CIÊNCIA DA COMPUTAÇÃO

#### Cristiano Vicente

# LABORATÓRIO REMOTO PARA PROTOTIPAÇÃO DE CIRCUITOS DIGITAIS UTILIZANDO KITS DE DESENVOLVIMENTO FPGAS XILINX.

Banca examinadora da monografía apresentada ao Curso de Bacharelado em Ciência da Computação do UNIVEM/F.E.E.S.R., para obtenção do Título de Bacharel em Ciência da Computação.

Marília, 05 de dezembro de 2016.

VICENTE, Cristiano. Laboratório remoto para prototipação de circuitos digitais

utilizando kits de desenvolvimento FPGAs Xilinx. 2016. 71f. Trabalho de curso.

(Bacharelado em Ciência da Computação) - Centro Universitário Eurípides de Marília,

Fundação de Ensino "Eurípides Soares da Rocha", Marília, 2016.

Resumo

O Laboratório Remoto, é uma plataforma web para auxiliar na prototipação de circuitos digitais

utilizando kits de desenvolvimento FPGAs remotamente, onde o usuário pode enviar o seu

projeto sintetizado pela ferramenta da Xilinx para o laboratório remoto online o projeto enviado

é programado no FPGA do kit de desenvolvimento no servidor, que retorna o resultado visual

do dispositivo físico e também permite o seu controle através da interface da plataforma na

web, com objetivo de facilitar o acesso aos dispositivos FPGAs e prover um laboratório remoto

interativo de baixo custo, acessível, de fácil manutenção e implantação, para fins educacionais,

para alunos e professores de graduações (e.g. Engenharia Elétrica e Ciência da Computação),

que fazem uso da tecnologia FPGA no desenvolvimento prático de disciplinas e projetos de

circuitos digitais, assim como alunos e professores engajados em pesquisas na área de

desenvolvimento de hardware, que não possuam à sua disponibilidade um kit de

desenvolvimento FPGA para testar seus projetos e verificar seus resultados.

Palavras-chave: FPGA, Laboratório Remoto, Programação Remota.

VICENTE, Cristiano. Laboratório remoto para prototipação de circuitos digitais

utilizando kits de desenvolvimento FPGAs Xilinx. 2016. 71f. Trabalho de curso.

(Bacharelado em Ciência da Computação) - Centro Universitário Eurípides de Marília,

Fundação de Ensino "Eurípides Soares da Rocha", Marília, 2016.

Abstract

The Remote Lab is a web platform to assist in the prototyping of digital circuits remotely with

FPGAs development boards, where the users may send their project synthesized by Xilinx's tool

to the online remote lab, the project sent is programmed in the FPGA development board by

the server, which returns the visual result of the physical device and also allow its control

through the web platform's interface, in order to facilitate access to FPGAs devices, providing

a low-cost and accessible, easy-to-maintain and inexpensive interactive remote lab for

educational purposes, for students and teachers from courses (e.g. Electrical Engineering and

Computer Science), which use FPGA technology in the development of practical learning and

projects of digital circuits, as well as students and teachers engaged in research of hardware

development, which might not have at their disposal a FPGA development kit to test their

projects and check their results.

**Keywords:** FPGA, Remote Lab, Remote Programing

# Lista de Figuras

| Figura 1 – Arquitetura básica de um FPGA                                  | 14 |

|---------------------------------------------------------------------------|----|

| Figura 2 – Diagrama de fluxo de projeto FPGA.                             | 18 |

| Figura 3 – Kit de desenvolvimento Digilent Nexys3                         | 19 |

| Figura 4 – UART, fluxo de dados serial                                    | 22 |

| Figura 5 – Laboratório remoto Vicilogic do autor Morgan, F                | 29 |

| <b>Figura 6</b> – Aplicação desktop viciLab do autor Morgan, F            | 30 |

| Figura 7 – Visão geral da arquitetura do Laboratório Remoto               | 32 |

| Figura 8 - Mapa das view/interfaces lado cliente.                         | 33 |

| Figura 9 – Tela de Login e cadastro.                                      | 34 |

| Figura 10 – Tela inicial do laboratório.                                  | 34 |

| Figura 11 – Tela de configurações                                         | 35 |

| Figura 12 – Tela de downloads.                                            | 36 |

| Figura 13 – Tela de upload do arquivo bit                                 | 36 |

| Figura 14 – Tela de simulação, controle e visualização do Kit FPGA        | 37 |

| Figura 15 – Estrutura completa de diretórios do servidor                  | 38 |

| Figura 16 – Arquivos de dependências package.json e bower.json            | 39 |

| Figura 17 – Estrutura de diretórios base gerado pelo express-generator    | 41 |

| Figura 18 – Diretórios do ORM Sequelize                                   | 43 |

| Figura 19 – Modelo do banco de dados.                                     | 44 |

| Figura 20 – Bibliotecas desenvolvidas para o projeto                      | 46 |

| Figura 21 – Fluxograma da view bit_upload                                 | 49 |

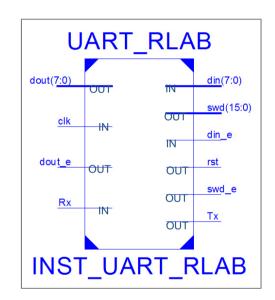

| Figura 22 – Componente UART_RLAB                                          | 50 |

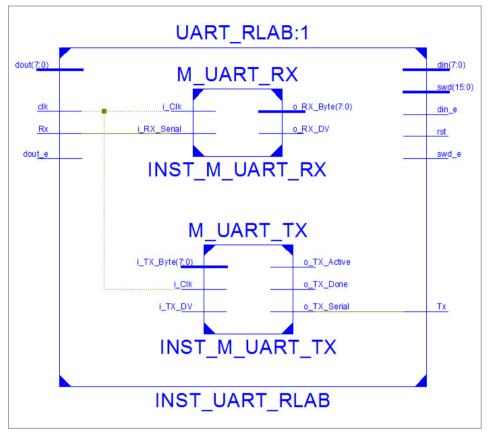

| Figura 23 – Visão dos componentes Rx e Tx instanciados no UART_RLAB       | 53 |

| Figura 24 – Máquina de estados do UART_RLAB que trata os dados de entrada | 54 |

| Figura 25 – IDE de desenvolvimento IntelliJ IDEA 2016.2.5.                | 57 |

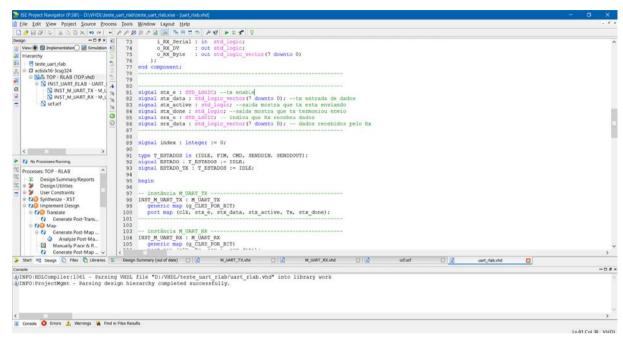

| Figura 26 – IDE desenvolvimento ISE Design Suite 14.5                     | 59 |

### Lista de Tabelas

| <b>Tabela 1</b> – Famílias de FPGAs Xilinx | 16 |

|--------------------------------------------|----|

| Tabela 2 – Estados do módulo UART_RLAB     | 55 |

# Lista de siglas

| AJAX  | Asynchronous Javascript and XML                    |

|-------|----------------------------------------------------|

| API   | Application Programming Interface                  |

| ASCII | American Standard Code for Information Interchange |

| CI    |                                                    |

| CSS   |                                                    |

| E/S   | Entrada e Saída                                    |

| FPGA  | Field Programmable Gate Arrays                     |

| HTML  | Hypertext Markup Language                          |

| IDE   | Integrated Development Environment                 |

| JSON  | JavaScritp Object Notation                         |

| LED   | Light Emissor Diode                                |

| ORM   | Object-relational mapping                          |

| RISC  | Reduced Instruction Set Computer                   |

| UART  | Universal Asynchronous Receiver/Transmitter        |

| UCF   | User Constraints File                              |

| USB   | Universal Serial Bus                               |

| VCS   |                                                    |

| VHDL  | VHSIC Hardware Description Language                |

| VHSIC | Very High Speed Integrated Circuit                 |

|       |                                                    |

### Sumário

| Introdu | ção                                                   | 10 |

|---------|-------------------------------------------------------|----|

| Objetiv | 0                                                     | 10 |

| Metodo  | logia                                                 | 11 |

| Materia | is                                                    | 12 |

| Organiz | zação do trabalho                                     | 12 |

| 1. Con  | ntextualização                                        | 14 |

| 1.1.    | Tecnologia FPGA                                       | 14 |

| 1.2.    | Principais fabricantes                                | 15 |

| 1.3.    | Xilinx                                                | 16 |

| 1.3.1.  | Famílias de FPGAs                                     | 16 |

| 1.3.2.  | Softwares e ferramentas de desenvolvimento para FPGA  | 17 |

| 1.4.    | Kit de desenvolvimento FPGA                           | 18 |

| 1.4.1.  | Kits de desenvolvimento Xilinx                        | 19 |

| 1.4.2.  | Kits de desenvolvimento Digilent Inc                  | 19 |

| 1.5.    | Linguagens de descrição de hardware (HDL)             | 20 |

| 1.5.1.  | Linguagem VHDL                                        | 20 |

| 1.5.2.  | Linguagem VERILOG                                     | 21 |

| 1.6.    | Sobre UART                                            | 21 |

| 1.7.    | Tecnologias web, cliente/servidor e interface gráfica | 22 |

| 1.7.1.  | Lado servidor com Node.js                             | 23 |

| 1.7.2.  | Google motor V8                                       | 23 |

| 1.7.3.  | Framework Express.js para Node.js                     | 24 |

| 1.7.4.  | Linguagem de programação JavaScript                   | 24 |

| 1.7.5.  | Lado cliente e interface gráfica.                     | 25 |

| 1.7.6.  | Câmeras IP                                            | 25 |

| 1.7.7.  | Persistência de dados                                 | 26 |

| 2. Tra  | balhos correlatos                                     | 27 |

| 3. Arc  | quitetura                                             | 32 |

| 3.1.    | Estrutura do lado cliente.                            | 33 |

| 3.1.1.  | Tela de cadastro e login                              | 33 |

| 3.1.2.  | Tela inicial index                                    | 34 |

| 3.1.3.  | Tela de configurações:                                | 34 |

| 3.1   | .4. Tela download                                            | 35 |

|-------|--------------------------------------------------------------|----|

| 3.1   | .5. Tela bit_upload:                                         | 36 |

| 3.1   | .6. Tela de simulação, controle e visualização, lab_area     | 37 |

| 3.2   | . Arquitetura do lado servidor                               | 38 |

| 3.2   | .1. Dependências                                             | 39 |

| 3.2   | .2. Estrutura do express.js                                  | 41 |

| 3.2   | .3. ORM Sequelize, models e banco de dados                   | 42 |

| 3.2   | .4. Bibliotecas desenvolvidas para o projeto                 | 44 |

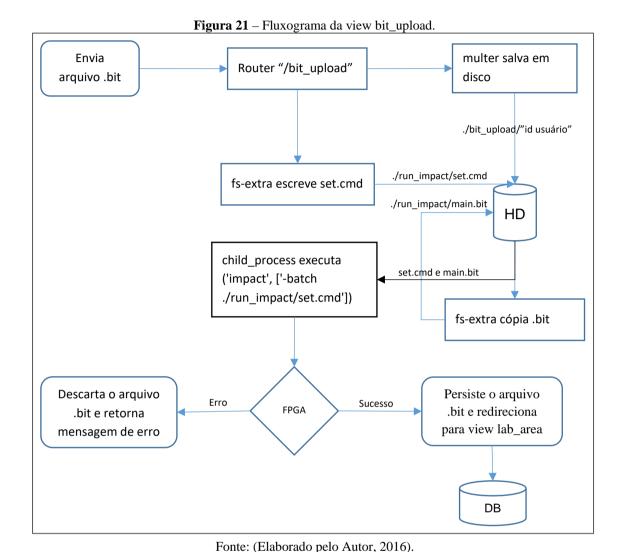

| 3.2   | .5. Gerenciamento do envio do arquivo bit, rota "Bit_upload" | 48 |

| 3.3   | . Conexão com o kit de desenvolvimento FPGA                  | 50 |

| 3.3   | .1. Protocolo de comunicação                                 | 54 |

| 3.4   | . Conexão com câmera IP                                      | 56 |

| 4. I  | mplementação e implantação                                   | 57 |

| 4.1   | . Lado cliente e servidor                                    | 57 |

| 4.2   | . Módulo UART VHDL                                           | 58 |

| 4.3   | . Implantação do Laboratório Remoto                          | 59 |

| 4.3   | .1. Compatibilidade                                          | 59 |

| 4.3   | .2. Processo de implantação                                  | 61 |

| 5. (  | Conclusão                                                    | 63 |

| 5.1.  | Dos Resultados                                               | 63 |

| 5.2.  | Das dificuldades no desenvolvimento                          | 64 |

| 5.3.  | Das limitações do projeto desenvolvido                       | 65 |

| 5.4.  | Para trabalhos futuros                                       | 66 |

| Refer | rências                                                      | 67 |

#### Introdução

Um laboratório tem um papel fundamental para o desenvolvimento do aprendizado em diversas disciplinas, onde pode ser demonstrado, simulado e provado em prática, diversos conceitos e teorias da ciência, por meio de ferramentas específicas para cada área de conhecimento enriquecendo o aprendizado e também auxiliando na pesquisa e busca por novos conhecimentos, assim também para o desenvolvimento de novas tecnologias.

A definição de laboratório é um local ou sala especial de trabalho, experimentação e investigações científicas, equipada com aparelhagem específica para pesquisa e experimentos. (cf. Michaelis, Dicionário Brasileiro da Língua Portuguesa, 2016). Este trabalho aborda um laboratório diferenciado de sua definição comum, no conceito de local ou sala física, mas como uma plataforma acessível através da web com equipamentos específicos para as disciplinas de circuitos digitais e arquitetura de computadores.

O autor J. S. Pastor et al. (2004), também propôs a utilização de acesso remoto para aprendizado na disciplina de Arquitetura de Computadores em seu trabalho (*A Remote Laboratory for Debugging FPGA*) e também cita a importância da prática de estudos em laboratórios.

É comumente aceito que experimentos em laboratórios são partes essências para o aprendizado nos cursos de Engenharia Elétrica e Ciência da Computação. Princípios básicos sobre Arquitetura de Computadores podem ser estudados com exemplos reais. (J. S. Pastor et al., 2004, tradução nossa).

#### **Objetivo**

Em suma, o objetivo deste trabalho é a criação de um laboratório remoto, em forma de uma plataforma web, para auxiliar na programação de circuitos digitais utilizando kits de desenvolvimento FPGAs de forma remota, através da plataforma web. Este projeto, visa um desenvolvimento de um laboratório de baixo custo e fácil manutenção, acessível e de fácil implantação, que permita ao usuário da plataforma ou laboratório remoto, poder enviar seu projeto VHDL já sintetizado pela ferramenta da Xilinx, o arquivo bit, para o laboratório remoto online, onde é programado no FPGA do kit de desenvolvimento no servidor e que também permite o controle do FPGA através da própria plataforma online.

#### Metodologia

Os métodos para o desenvolvimento deste projeto foram organizados em:

- Levantamento bibliográfico, pesquisa de trabalhos correlatos e tecnologias: Foi realizado pesquisas sobre laboratório de acesso remoto e laboratórios de acesso remoto para circuitos digitais com FPGA, também foi realizado pesquisas de tecnologias a serem utilizadas para a comunicação do FPGA com o servidor utilizando a porta serial e tecnologias para transmissão de vídeo.

- Levantamento de tecnologias a serem utilizadas para o desenvolvimento do projeto: Foi realizado um estudo sobre as tecnologias web, para escolha da tecnologia a ser utilizada no desenvolvimento do servidor, que foi definido o Node.js para o servidor, também foi realizado um estudo específico nas bibliotecas e métodos nativos da tecnologia escolhida para o servidor, para o correto desenvolvimento do módulo de comunicação entre o FPGA e o servidor.

- Implementação inicial do servidor e do lado cliente com controle de acesso: Foi

implementado a estrutura básica do servidor com login e cadastro de usuários para o

laboratório.

- Desenvolvimento da comunicação entre o servidor e o kit de desenvolvimento FPGA:

foi desenvolvido um módulo VHDL, um módulo de comunicação serial no servidor e o

protocolo de comunicação, utilizando o módulo serialport para Node.js e os estudos e

análises levantados sobre o funcionamento do módulo serialport e o método nativo

Buffer do Node.js para trabalhar com dados binários.

- Desenvolvimento da plataforma de controle, programação e visualização do Laboratório Remoto lado servidor e cliente: foi desenvolvido o streaming de vídeo utilizando câmeras IP, a interface de controle do FPGA foi implementada em cima do módulo de comunicação que foi desenvolvido e a implementação do reconhecimento e programação do kit de desenvolvimento utilizando a ferramenta iMPACT da Xilinx e pôr fim a interface de usuário para o lado cliente do laboratório.

#### **Materiais**

Este item lista os materiais utilizados para a implementação do projeto:

- Banco de dados MySQL.

- Bootstrap e JQuery, framework e biblioteca *frontend*.

- Computador tipo laptop com sistema operacional Windows 10, utilizado no desenvolvimento de todo o projeto.

- Digilent Nexys3, Kit de desenvolvimento FPGA.

- Express.js, framework *backend* para Node.js

- Ferramenta iMPACT, ferramenta do pacote de *software* da Xilinx, utilizado para reconhecer o kit de desenvolvimento FPGA conectado e fazer sua programação.

- IDE de desenvolvimento IntelliJ IDEA Ultimate 2016.2, utilizado no desenvolvimento do lado servidor e cliente.

- IDE de desenvolvimento Xilinx ISE Design Suite 14.5, utilizado para o desenvolvimento do módulo VHDL.

- Módulos SerialPort e Request, para Node.js

- Módulos VHDL, receptor e transmissor, utilizados no módulo UART de Merrick (2016).

- Node.js e seus módulos nativos.

- ORM Sequelize.

- Smartphone Android com aplicativo IPCam, que simula uma câmera IP utilizando a câmera do smartphone.

#### Organização do trabalho

Este trabalho está organizado em cinco capítulos, sendo:

- 1- Contextualização: Neste capítulo é feito a contextualização e fundamentação teórica das tecnologias utilizadas no projeto.

- 2- Trabalhos correlatos: Neste capítulo foi descrito os trabalhos correlatos que propõem o desenvolvimento de um laboratório de acesso remoto e relatam seus benefícios.

- 3- Arquitetura: Este capítulo aborda a estrutura e a arquitetura do projeto e como funciona os componentes e módulos do Laboratório Remoto e as suas comunicações.

- 4- Implementação e implantação: Este capítulo aborda o processo de implementação e implantação do projeto e as tecnologias e ferramentas utilizadas.

- 5- Conclusão: Este capítulo relata os resultados atingidos, as dificuldades no desenvolvimento do projeto, suas limitações e oportunidades para trabalhos futuros.

#### 1. Contextualização

Este capítulo tem como objetivo apresentar e contextualizar as tecnologias e ferramentas utilizadas no projeto e também apresentar brevemente tecnologias similares ou concorrentes às utilizadas no projeto quando disponíveis, sem se aprofundar muito em suas fundamentações teóricas e técnicas, são abordados os seguintes itens:

- Tecnologia FPGA e os principais fabricantes de FPGA.

- Modelos de FPGAs, ferramentas e softwares do fabricante Xilinx.

- Kit de desenvolvimento FPGA

- Linguagens de descrição de Hardware (HDL)

- Comunicação serial UART.

- Tecnologias de desenvolvimento web e servidor, linguagem de programação,

frameworks, persistência dedados e dispositivos de transmissão de vídeo. (Câmera IP).

#### 1.1. Tecnologia FPGA

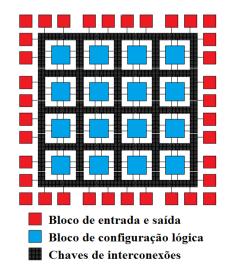

O FPGA (*Field Programmable Gate Arrays*), é um circuito integrado composto de uma matriz de blocos lógicos configuráveis conectados através de interconexões programáveis, este circuito integrado é bastante flexível e pode ser programado e reprogramado, possibilitando criar um número ilimitado de circuitos para diversas aplicação ou funções desejadas.

Figura 1 – Arquitetura básica de um FPGA

Fonte: Tecnologia de FPGA, MEDEIROS, D. S., 2016

Na Figura 1 a arquitetura básica, onde pode-se ver uma matriz de blocos ou células lógicas que são conectadas através do barramento de interconexões e por fim são ligados aos blocos de entradas e saídas. As células lógicas comportam lógicas simples e conectadas através do barramento de interconexões, formam lógicas complexas, podendo simular vários outros circuitos de apoio e até mesmo um processador simples, assim sendo uma ferramenta flexível e muito poderosa, para auxiliar na simulação em *hardware* e desenvolvimento de protótipos de outros circuitos integrados.

Segundo Maxfield, Clive (2004), no início da década de 90, os FPGAs eram utilizados principalmente nos sistemas de redes e de telecomunicações e logo ao fim da década de 90 já estavam sendo utilizados nos setores automotivos e em diversas aplicações industriais.

Atualmente os FPGAs, são utilizados nas mais diversas áreas, citando algumas, tais como; Aeroespacial, Segurança, Computação de Alta Performance, Processamento de Áudio, Vídeo e Imagens, equipamentos na área de Medicina, pesquisas Cientificas e Acadêmicas, entre outras diversas áreas no desenvolvimento de protótipos de CIs, devido a sua flexibilidade de desenvolvimento e baixo custo.

A maior parte do custo de um processador, micro controlador ou um chip qualquer está em seu desenvolvimento e esta tecnologia trouxe um avanço considerável para o desenvolvimento de protótipos de circuitos integrados para produção em massa e até mesmo a criação de chips únicos, utilizando o próprio FPGA como produto final, não sendo necessário passar por todo o processo de produção para um único chip.

#### 1.2. Principais fabricantes

O primeiro FPGA comercial foi lançado em 1985 pela Xilinx, (*Funding Universe* apud *International Directory of Company Histories*, Vol. 16. St. James Press, 1997), o atual líder do mercado de FPGAs seguido pela sua maior concorrente, a Altera, que tiveram um grande crescimento na década de 80, pela enorme demanda do mercado pela tecnologia do FPGA.

Segundo informações publicadas no site *Electronic Engineering Journal* por Morris, Kevin (2014), os dois fabricantes, Xilinx e Altera controlavam aproximadamente 90% do mercado de FPGAs em 2014, sendo a Xilinx com a maior parcela, tendo sozinha aproximadamente 45% a 50% do mercado, os outros 10% do mercado são compartilhados entre; Achronix, Atmel, e2v, Lattice Semiconductor, MicroSemi (Actel), Tabula e demais fabricantes menores.

No ano de 2016 foi publicado um novo artigo no site *Electronic Engineering Journal*, também por Morris, Kevin (2016), "Xilinx vs Intel", no qual relata a aquisição do fabricante Altera pela Intel, que é o maior fabricante de semicondutores do mundo, segundo relatório publicado no site ICinsights (2016), Morris conclui em seu artigo, que apesar de a Xilinx possuir uma liderança significativa no mercado de FPGAs no momento, a Xilinx é uma empresa muito menor do que a agora combinada Intel/Altera, porém ainda dominante até que esta grande aquisição se estabilize.

#### 1.3. Xilinx

Para o desenvolvimento deste trabalho, será utilizado um kit de desenvolvimento com FPGA do fabricante Xilinx e seus softwares, as informações a seguir terão maior enfoque nos dispositivos FPGAs e softwares da Xilinx.

#### 1.3.1. Famílias de FPGAs

Como os FPGAs são utilizados hoje em dia nas mais diversas áreas da tecnologia, eles são divididos em famílias ou séries, existem FPGAs desde uso geral há fins específicos.

Tabela 1 – Famílias de FPGAs Xilinx

| Portfólio da Família de FPGAs Xilinx |          |                        | Família Adicional |               |                      |               |            |

|--------------------------------------|----------|------------------------|-------------------|---------------|----------------------|---------------|------------|

| 45nm                                 | 28nm     | 20nm                   | 16nm              | Automotiva    | Defesa<br>Militar    | Aeroespacial  |            |

| Spartan-6                            | Artix-7  | Kintex                 | Kintex            | XA Artix-7    | Virtex-<br>7Q        | Virtex-5QV    |            |

| Spartari-0                           | Altix-7  | UltraScale UltraScale+ | XA Spartan-6      | Kintex-<br>7Q | VIITEX-3QV           |               |            |

| Artix-7                              | Kintex-7 | Virtex                 | Virtex            | XA Spartan-3A | Artix-7Q             | V" - 40V      |            |

| Arux-7                               | AI UX-7  | KIIILEX-7              | UltraScale        | UltraScale+   | XA Spartan-3A<br>DSP | Virtex-<br>6Q | Virtex-4QV |

| Zinq                                 | Virtex-7 |                        |                   | VA Spartan 2E | Spartan-<br>6Q       |               |            |

| ZIIIY                                |          |                        | 15 11 5           | XA Spartan-3E | Virtex-<br>5Q        |               |            |

Fonte: Xilinx Inc, All Programmable FPGAs and 3D ICs, 2016

Atualmente a Xilinx conta com 5 modelos base e uma família especial adicional, assim como ilustrado na Tabela 1, (*Spartan 6, Artix 7, Zynq, Kintex 7 e Virtex 7*), divididos em grupos ou famílias de acordo com suas escalas, que são os; *Low-End 45nm, 7 Series 28nm, UlraScale 20nm* e *UlraScale+ 16nm*, e a família adicional para fins mais específicos, que são as séries Automotiva, Defesa (militar e comercial) e aeroespacial.

Para fins de conhecimento, a Altera, maior concorrente direto da Xilinx, conta também com uma família de FPGAs; *Stratix Series, Arria Series, Cyclone Series* e *MAX Series*, cada família com diversos modelos de uso geral e outros voltados para fins específicos assim como a Xilinx.

#### 1.3.2. Softwares e ferramentas de desenvolvimento para FPGA

Além do mercado de semicondutores, a Xilinx conta também com softwares específicos, para auxiliar no desenvolvimento com os dispositivos FPGAs, o seu atual pacote para desenvolvimento é o *Vivado Design Suite*, este voltado para nova família de FPGAs da série 7, tais como; Artix 7, Kintex 7 e Virtex 7 e o ISE Design Suite voltados para dispositivos da série 6 como o Spartan 6 e FPGAs das gerações anteriores a este.

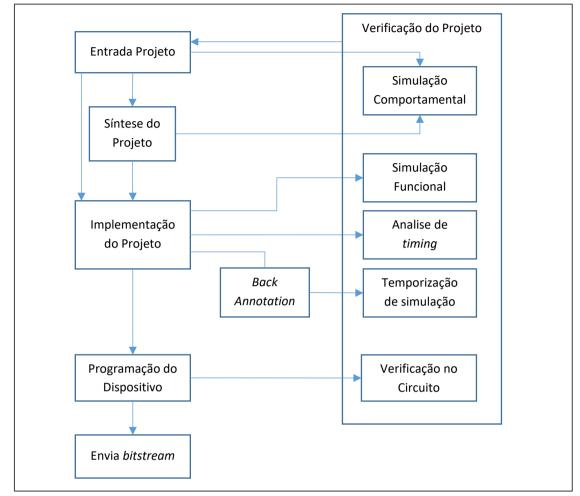

No fluxograma da Figura 2, o fluxo de projeto segue com a entrada do projeto que são modelos de descrição de hardware, que podem ser descritos nas linguagens Verilog, VHDL, UCF ou ABEL, após a entrada, segue para verificação e síntese do projeto, onde é feito a checagem de sintaxe, simulação comportamental e mapeamento da tecnologia, na implementação do projeto é feita a tradução do projeto para o dispositivo, o mapeamento para os recursos disponíveis do dispositivo, criação das rotas e geração do arquivo de programação *bitstream* para o dispositivo alvo. (Xilinx Inc., 2016).

Após gerado o arquivo de programação *bitstream*, é feita a programação do dispositivo através do iMPACT, é uma ferramenta presente nos pacotes de desenvolvimento da Xilinx, apresentado em batch ou interface de usuário, o iMPACT permite a configuração direta dos dispositivos FPGAs da Xilinx que estão conectados ao PC, faz a verificação de compatibilidade do projeto com o dispositivo, executa configuração inicial e envio do *bitstream* para o dispositivo e depuração de erros (Xilinx Inc., 2016).

O iMPACT será uma das ferramentas utilizadas para concepção deste trabalho, o webservice do Laboratório Remoto, chamará o iMPACT via batch que executará a verificação dos dispositivos FPGAs conectados no servidor e fazer sua configuração e programação.

Figura 2 – Diagrama de fluxo de projeto FPGA.

Fonte: Xilinx Inc, FPGA Design Flow Overview, 2016

#### 1.4. Kit de desenvolvimento FPGA

Os FPGAs consistem apenas no circuito integrado, que podem ser acoplados em placas de desenvolvimento *protoboards* ou diretamente a um equipamento que fará uso do chip.

Para auxiliar no desenvolvimento e melhorar a produtividade, a Xilinx e algumas empresas comercializam o FPGA já acoplado a um kit de desenvolvimento, com vários componentes acoplados, como *displays*, LEDs, botões e vários tipos de entradas e saídas, como áudio, vídeo, USB, VGA, HDMI, RJ45, etc, facilitando os testes e simulações de aplicações desenvolvidas.

#### 1.4.1. Kits de desenvolvimento Xilinx.

A Xilinx fornece uma grande quantidade de kits de desenvolvimento para diversas categorias e áreas, como kits para iniciantes, projetos de baixo custo e projetos de alto custo e computação de alto desempenho.

Assim como possuem FPGAs para diversas áreas, também cotam com kits de desenvolvimento para essas áreas como; médica, industrial, automotiva, aeroespacial, defesa, áudio e vídeo, telecomunicações e etc. os kits de desenvolvimento para as áreas específicas possuem componentes, módulos e acessórios específicos voltados para a área designada.

#### 1.4.2. Kits de desenvolvimento Digilent Inc.

A Digilent, é uma empresa de produtos para Engenharia Elétrica, servindo estudantes, universidades e empresas, sua missão é fazer com que as tecnologias de engenharia e design elétricos sejam compreensíveis e acessíveis a todos, fornecendo ferramentas educacionais relevantes para a indústria e universidades (Digilent Inc, 2016).

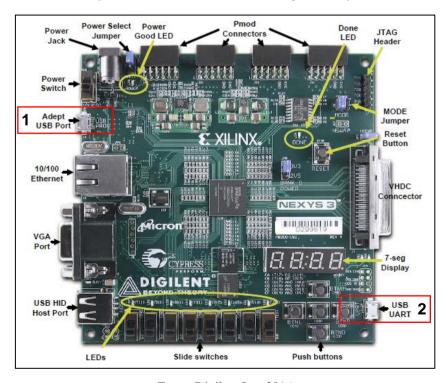

Figura 3 – Kit de desenvolvimento Digilent Nexys3

Fonte: Digilent Inc, 2016

Para o desenvolvimento deste trabalho, será utilizado um Kit de desenvolvimento *Nexys3*, fabricado pela Digilent Inc, utilizando o FPGA Spartan-6 LX16 fabricado pela Xilinx, que vem acoplado a placa do kit, este projeto é compatível não somente com este kit de desenvolvimento, mas também com todos os kits de desenvolvimento para FPGAs da 6ª geração, suportados pela ferramenta iMPACT do pacote de *softwares* ISE Design Suite.

Na Figura 3 é ilustrado uma visão da placa do kit de desenvolvimento Nexys3 e seus componentes de entrada e saída e este kit conta também com 48Mbytes de memória não volátil, no centro da placa encontra-se o CI do FPGA, um Xilinx Spartan-6 LX16 de 324 pinos, que opera a 100MHz, que é conectado diretamente a maior parte dos componentes da placa.

Na Figura 3, destacados por retângulos numerados estão as duas portas USB que são conectadas diretamente na máquina do servidor, sem a necessidade de qualquer outro hardware adicional, a porta *Adept USB Port/USB Prog* (retângulo 1) é a porta utilizada para fazer a identificação e programação do kit de desenvolvimento, a outra porta (retângulo 2), *USB UART* é utilizada para se comunicar com o servidor através um módulo implementado em VHDL que faz a comunicação de entrada e saída entre FPGA e o servidor do laboratório.

#### 1.5. Linguagens de descrição de hardware (HDL)

As HDLs, linguagens de descrição de hardware, são linguagem semelhantes às linguagens de programação, porém são orientadas a descrição da estrutura e do comportamento do hardware, tendo grande vantagem em comparação à esquemática do projeto de um hardware, pois podem representar diretamente equações booleanas, tabelas verdade e operações complexas, de forma fácil de ser interpretado. (Midorikawa, Edson T., 2001).

#### 1.5.1. Linguagem VHDL

O nome VHDL (*VHSIC Hardware Description Language*), e o termo VHSIC (*Very High Speed Integrated Circuit*), em tradução livre sendo "linguagem de descrição de hardware para circuitos integrados de velocidade muito alta".

A linguagem VHDL foi originalmente desenvolvida em 1980, por empresas contratadas pelo Departamento de Defesa dos Estados Unidos, com o propósito de criar uma HDL

padronizada, no ano de 1987, o Departamento de Defesa designou que todos os circuitos eletrônicos digitais fossem descritos em VHDL, (PEREIRA, Fábio Dacêncio, et al, 2003).

O *Institute of Electrical and Electronics Engineers* (IEEE), ratificou o primeiro padrão do VHDL, o (Padrão 1076-1987 ou VHDL 87), que foi atualizado em 1993: (Padrão 1076-1993 ou VHDL 93) e sua última atualização foi em 2008, atual (Padrão 1076-2008), (*IEEE Standard VHDL Language Reference Manual*, 2009).

A estrutura mínima de um projeto descrito em VHDL requer uma declaração de entidade (*entity*) e uma arquitetura (*arquiteture*). A *entity* é a parte principal do projeto que define os aspectos externos, descreve as entradas e saídas, largura de barramento, funções e como ocorre a transferência de informações. O nome de uma *entity* deve identificar o projeto, podendo usar letras e números, porém deve iniciar por uma letra. A *arquiteture* define os aspectos internos, onde são descritas todas as lógicas operacionais, atribuições, comparações e como se relacionam com outros sinais internos.

#### 1.5.2. Linguagem VERILOG

A linguagem Verilog foi introduzida em 1985 pela *Gateway Design Automation* e em 1989, a Gateway foi comprada pela empresa *Cadence Design Systems*, que tornou a linguagem de domínio público em maio de 1990 com a formação da *Open Verilog International* (OVI).

O Verilog foi ratificado pelo IEEE, sendo Verilog-95 (padrão IEEE 1364-1995), Verilog 2001 (IEEE 1364-2001) e Verilog 2005 (IEEE 1364-2005). O Verilog tem uma grande semelhança com a linguagem de programação C. (Midorikawa, Edson T., 2001, p. 3).

#### 1.6. Sobre UART

O significado de UART é *Universal Asynchronous Transmitter/Receiver*, Transmissor e Receptor Universal Assíncrono, é um componente de hardware tipicamente encontrado em dispositivos com portas seriais assíncronas, utilizado para converter dados entre comunicações seriais e paralelas. Alguns exemplos de portas controladas pelas UARTs; Porta Serial RS232, eram padrão em PCs e outros dispositivos antes de as USB se tornarem comuns; Portas seriais que são conectados ao PC por um módulo conversor USB (AXELSON, J., 2007);

Portas que se conectam a um PC através de um conversor USB que usa um driver que atribui uma porta COM para o dispositivo. Os conversores estão disponíveis como módulos e como chips para incorporação em circuitos. Um conversor pode converter entre USB e RS-232, RS-485, TTL serial, ou mesmo uma interface paralela. (AXELSON, J., 2007)

Esta última citação de AXELSON, J., é a forma em que o UART é utilizado neste projeto, um módulo UART é implementando no FPGA e conectado através da porta USB UART do kit de desenvolvimento à porta USB do PC servidor, que converte os dados seriais transmitidos pela USB em *full-duplex*, (transmite nas duas direções, cada um com sua linha, receptor e transmissor ou Rx/Tx).

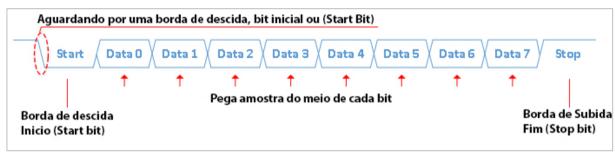

Figura 4 – UART, fluxo de dados serial

Fonte: (NANDLAND, 2016)

Na Figura 4 é apresentado o fluxo de dados do receptor serial UART, de característica assíncrona, este fica em estado de espera até que recebe o bit inicial ou *Start bit*, para iniciar a detecção de um byte em uma cadeia de 10 bits, 1 bit inicial, 8 bits de dados e 1 bit final, ao fim da detecção este tem em sua saída, e.g. Out[7,0] a cadeia inteira de bits que formam o byte enviado, que podem ser lidos agora em paralelo.

O envio através do transmissor é feito de forma similar, este quando recebe uma cadeia de bits a serem enviados, primeiro este emite o *start bit* ou bit inicial e depois transfere bit a bit a cadeia a ser enviada finalizando com 1 *stop bit*.

#### 1.7. Tecnologias web, cliente/servidor e interface gráfica.

As informações deste tópico descrevem as tecnologias web utilizadas no desenvolvimento do lado servidor e cliente. O lado servidor deste trabalho foi desenvolvido utilizando a linguagem de programação JavaScript para Node.js com *framework* Express e lado

cliente ou interface gráfica, é uma aplicação desenvolvido em forma de website utilizando as atuais tecnologias web, que serão descritos nos sub tópicos seguintes.

#### 1.7.1. Lado servidor com Node.js

Node.js é um ambiente de E/S não bloqueante assíncrono e orientado a eventos, construído sobre o motor V8 de JavaScript do Google. Node.js foi projetado para criar aplicativos de rede escaláveis para muitas conexões que podem ser manipuladas simultaneamente.

Node.js é semelhante a projetos e influenciado por sistemas como *Ruby's Event Machine* ou *Python's Twisted*. O Node.js leva o modelo de evento um pouco mais, ele apresenta um *loop* de evento como uma construção em tempo de execução em vez de como uma biblioteca. Em outros sistemas há sempre uma chamada de bloqueio para iniciar o ciclo de eventos. Normalmente, o comportamento é definido através de *callbacks*, que são funções passadas como parâmetro de outra função quando um evento acontece, no início de um script e no final, inicia um servidor através de uma chamada de bloqueio como *EventMachine::run()*.

No Node.js não existe tal chamada de inicie-o-laço-de-evento, o Node.js simplesmente entra no *loop* de eventos depois de executar o script de entrada e sai do *loop* de eventos quando não há mais *callbacks* a executar, esse comportamento é como o JavaScript do navegador - o *loop* de eventos está oculto do usuário. O HTTP é uma entidade de primeira classe no Node, projetado com *streaming* e baixa latência em mente, isso torna o Node.js bem adaptado para a fundação de uma biblioteca ou *framework* da Web.

O ecossistema de pacotes do Node.js, "npm", é o maior ecossistema de bibliotecas de código aberto do mundo. (Node.js Foundation, 2016, tradução nossa).

#### 1.7.2. Google motor V8

Como parte fundamental da tecnologia de construção do Node.js este item descreve um pouco desta tecnologia. O Goolge V8 é um interpretador de JavaScript de alta performance de código fonte aberto, escrito em C++ e utilizado principalmente no Google Chrome, navegador de código aberto do Google.

O V8 implementa o ECMAScript conforme especificado em ECMA-262 que define e padroniza linguagens de programação de propósito geral, o V8 roda nos sistemas, Microsoft Windows XP ou mais recente, Mac OS X 10.5+ e sistemas Linux que utilizam processadores do tipo IA-32, ARM ou MIPS e pode ser executado autônomo, ou pode ser incorporado em um aplicativo C++, assim como o Node.js.

O motor V8 compila e executa código-fonte em JavaScript, manipula alocação de memória para os objetos e o coletor de lixo desaloca os objetos que ele não precisa mais. O coletor de lixo *stop-the-world*, geracional e preciso do V8 é uma das chaves do desempenho do V8 (Google Developers, 2016, tradução nossa).

#### 1.7.3. Framework Express.js para Node.js

O Express é um projeto da Fundação Node.js, um *framework* JavaScript para Node.js mínimo e flexível que fornece um conjunto robusto de recursos para aplicações web e móvel que roda no lado servidor (StrongLoop, Inc e IBM, 2016).

Este framework é utilizado no servidor do Laboratório Remoto para a organização e construção de parte do lado cliente, ele controla as rotas "URL" de acesso e a renderização de parte das páginas web servidos no lado cliente.

#### 1.7.4. Linguagem de programação JavaScript

A JavaScript ou JS é uma linguagem de programação leve, interpretada e orientada a objetos com funções de primeira classe, [a linguagem JavaScript foi criada por Brendan Eich enquanto trabalhava na Netscape, e desde então foi atualizada para conformar-se ao padrão ECMA-262 Edition 5 e suas versões mais recentes], conhecida como a linguagem de *scripting* para páginas Web, mas também utilizada em muitos ambientes fora dos navegadores. (Mozilla Developer Network, 2016).

Outra aplicação comum para JavaScript é usá-lo como uma linguagem de *scripting* para o lado servidor (da Web). Um servidor web de JavaScript expõe objetos de *host* que representam uma solicitação HTTP e objetos de resposta, que são então manipulados por um programa em JavaScript que gera páginas web dinamicamente.

O Node.js é um exemplo popular deste tipo de uso, o Javascript é uma linguagem de *scripting* baseada em protótipos, multi-paradigma e dinâmica, suportando os estilos orientado a objetos, imperativo e funcional. (Mozilla Developer Network, 2016).

#### 1.7.5. Lado cliente e interface gráfica.

O lado cliente do Laboratório Remoto utiliza as tecnologias web atuais como, HTML5 que é a linguagem de marcação de hipertexto para apresentar e estruturar o conteúdo na web, CSS3 é a linguagem que define os estilos e dão aparência para as páginas web e a linguagem de programação JavaScritp, descrito no item 1.7.4, para controlar elementos da aplicação no lado cliente e sua comunicação com o servidor utilizando a técnica Ajax.

O lado cliente foi desenvolvido com o *framework* Bootstrap para parte visual, que é um *framework* para desenvolvimento *front-end* (lado cliente de aplicações web), de projetos responsivo para dispositivos móveis e na web. Este *framework* tem como dependência a biblioteca JQuery, que é uma biblioteca JavaScript de código aberto que conta com uma grande gama de recursos para facilitar a manipulação de páginas web. (Bootsrap, JavaScript Overview, 2016).

#### 1.7.6. Câmeras IP

Como foi proposto para este trabalho a visualização do Kit de desenvolvimento do FPGA por *streaming* de vídeo através da interface gráfica do usuário, foi adotado então a utilização de Câmeras IP para a transmissão de vídeo.

A câmera IP é um dispositivo de hardware para transmissão de vídeo através de uma rede IP, como LAN, Intranet ou Internet. Usando simplesmente um navegador web e uma conexão de Internet, pode-se convenientemente ter acesso ao vídeo de uma câmera IP, em alguns casos, até áudio, de qualquer local que esteja.

Os modelos atuais são compatíveis com as tecnologias Ethernet e Wi-Fi e são separadas em categorias como Pan/Tilt/Zoom que permite ao usuário mudar o ângulo das câmeras, habilitar áudio, controlar uso de luz infravermelha para uso noturno, entre outros.

É possível ainda instalar a câmera IP com os convencionais fios (cabo de rede) para streaming de áudio e vídeo ou utilizar tecnologia Wireless com criptografia. A vantagem é que

o sistema pode ser facilmente ampliado, com a utilização de hub's, que custam bem menos do que uma placa de captura de imagem das câmeras analógicas. (Sitehosting, 2016).

#### 1.7.7. Persistência de dados

As informações enviadas para o servidor como, contas de usuários, informações de configurações e informações de armazenamento do arquivo bit do projeto sintetizado pelo usuário, são persistidas pelo servidor utilizando um banco de dados relacional.

O banco de dados adotado para este projeto é o *MySQL Community Server*, "é o banco de dados de código aberto mais popular do mundo, que é suportado por uma comunidade ativa de desenvolvedores e entusiastas de código aberto", segundo (MySQL, 2016).

#### 2. Trabalhos correlatos

Laboratórios de acesso remoto para circuitos digitais utilizando dispositivos FPGAs através de uma conexão web, foram propostos por outras pesquisas anteriores, com o objetivo de maximizarem o tempo de uso e a facilidade de acesso aos laboratórios convencionais, dentre os trabalhos propostos há o trabalho do autor Trevelyan, J. para área de Engenharia Mecatrônica, onde o autor descreve as vantagens de um laboratório remoto e reforça a sua importância.

Segundo Trevelyan, J. (2004 apud (Goldberg 1999, Taylor e Trevelyan 1995, Henry 2003)), laboratórios de acesso remoto usando conexões de Internet, existem em forma de protótipo desde meados de 1990. Trevelyan, J. et al, em outubro de 1994, iniciaram na Universidade da Austrália Ocidental um laboratório online, o *Australia's Telerobot on the Web*.

O autor apresenta em seu artigo uma revisão das principais experiências que eles aprenderam desde 1994 a 2004 e descreve brevemente o *Telelabs*, um *framework* de custo efetivo que provê uma série extensível de laboratórios online que podem ser mantidos por um orçamento normal de operação. O laboratório de Trevelyan, J. et al entrou em funcionamento em 2002 e em 2003 continha 5 diferentes módulos, incluindo o seu primeiro laboratório online, o *Telerobot*.

A partir de 2002, Trevelyan, J. et al concentrou seu projeto na atividade de aprendizado efetivo para estudantes usando o laboratório online e avaliação da efetividade do aprendizado. O autor reporta em sua publicação os resultados dos ensaios com o laboratório remoto online como parte de um tutorial de exercícios semanais para graduandos do curto se engenharia Mecatrônica.

Os ensaios revelaram que os estudantes que usaram o laboratório de acesso remoto, operaram equipamentos por muito mais tempo do que em aula de laboratório convencional e como resultado tiveram o aprendizado melhorado consideravelmente. Isto permite aos estudantes tempo necessário para explorar as diferenças entre a teoria e o comportamento real dos equipamentos por conta própria.

Com a carga horaria obrigatória das aulas normais de laboratório, em maior parte tendem a seguirem uma sequência pré-determinada de medições, cálculos e escrita de relatórios, sem necessariamente entenderem o que eles estão fazendo. O estilo de interação com os equipamentos usando o laboratório de acesso remoto é muito mais representativo de um cenário típico industrial.

O autor Pastor, J. S. et al (2004), apresenta em seu artigo um framework para testar protótipos de microprocessadores. Um microprocessador RISC é projetado pelos estudantes utilizando a linguagem VHDL e adaptado para ser implementado em um dispositivo FPGA.

O correto comportamento do microprocessador projetado é verificado executando um programa de testes escrito e compilado pelos alunos para este microprocessador. Usando um cliente web, os usuários enviam um arquivo com o programa de testes e o projeto para um laboratório remoto, que são carregados em um dispositivo FPGA real. Um conjunto de ferramentas para depuração da execução remota dos testes foram desenvolvidos usando uma interface gráfica similar as demais ferramentas de depuração.

Grupos de estudantes do curso de Arquitetura de Computadores participaram deste experimento. As boas opiniões recebidas dos alunos, sugerem a incorporação dos experimentos do laboratório remoto no próximo curso regular.

Hashemian, R. e Riddley, J. (2007) propôs o FPGA e-Lab, uma técnica de acesso remoto ao laboratório para projetos e testes com FPGA, em seu artigo o autor ilustra o objetivo e importância do seu trabalho para educação em engenharia, com o enriquecimento da experiência de uso do laboratório permitindo aos estudantes mais tempo de uso do laboratório e também melhorando o aprendizado com experimentos complementares.

A técnica de acesso remoto proposta por R. Hashemian e J. Riddley é feita através do Assistente de Área de Trabalho Remota do Microsoft Windows XP, que permite o acesso remoto ao computador do laboratório que estará rodando uma aplicação desktop que mostra a imagem de um kit de desenvolvimento *Xilinx Spartan-3E Starter Kit*, por streaming de vídeo e permite o controle do dispositivo FPGA que está ligado ao computador do laboratório via uma interface gráfica interativa *LabView* e outros hardwares bem como porta serial RS-232 e cabo USB.

O autor Morgan, F. (2011), apresenta em seu artigo o projeto de um laboratório remoto para melhorar o aprendizado em sistemas digitais para os cursos de engenharia elétrica e eletrônica utilizando FPGAs. Morgan, F. também cita os benefícios descritos pelo autor Trevelyan, J. e ressalta a melhora do aprendizado pela aplicação da prática de "aprender fazendo", custos reduzidos, compartilhamento de recursos, flexibilidade e conveniência do tempo de uso do laboratório e melhoras da interação com o estudante permitindo novas técnicas pedagógicas. Morgan, F., até o ano de 2016 publicou 3 artigos sobre o laboratório remoto, em

seu primeiro artigo ele descreve os elementos do laboratório remoto e demonstra aplicações de utilização para apoiar o aprendizado.

O laboratório descrito por Morgan, F. em seu artigo, é composto basicamente por um módulo com um kit de desenvolvimento FPGA (Digilent Nexys 2) e uma webcam, ligados a um servidor USB e este conectado a um servidor web, sua arquitetura é expansível e suporta uma certa quantidade de pares de dispositivos FPGAs com sua respectiva webcam e servidor USB, o servidor web controla o acesso alocando uma sessão para cada usuário, permitindo o envio do projeto, a visualização e interação.

Morgan em seu terceiro artigo em 2014, definiu o seu laboratório remoto como RFL (Remote FPGA Lab), sendo uma aplicação baseada na web, com controles interativos para manuseamento de *hardwares* de circuitos lógicos configuráveis na nuvem em tempo real e oferecendo suporte a uma abordagem de aprendizado de sistemas digitais, antes disponível no website <a href="http://remoteFPGA.com">http://remoteFPGA.com</a>, que agora é redirecionado para: <a href="http://vicilogic.com/">http://vicilogic.com/</a>, referente ao mesmo projeto de Morgan, F. que foi renomeado para *Vicilogic* (VICILOGIC, 2016).

BUILD THE MOST POWERFUL HARDWARE IMAGINABLE

VICILEARN:

ONLINE INTERACTIVE LEARNING &

ASSESSMENT OF DIGITAL SYSTEMS

GET STARTED WITH VICILEARN

VICILAB:

DESIGN AND PROTOTYPE DIGITAL LOGIC

HARDWARE IN THE CLOUD, AND INTERACTIVE PROTOTYPE GUI

GET STARTED WITH VICILAB

VICILAB:

DESIGN AND PROTOTYPE GUI

GET STARTED WITH VICILAB

VICILAB:

DESIGN AND PROTOTYPE GUI

GET STARTED WITH VICILAB

VICILAB:

DESIGN AND PROTOTYPE GUI

GET STARTED WITH VICILAB

VICILAB:

DESIGN AND PROTOTYPE GUI

GET STARTED WITH VICILAB

VICILAB:

DESIGN AND PROTOTYPE GUI

GET STARTED WITH VICILAB

VICILAB:

DESIGN AND PROTOTYPE GUI

MAZI Cumpowent Symbol

MAZI Cumpow

Figura 5 – Laboratório remoto *Vicilogic* do autor Morgan, F.

Fonte: (Próprio autor, 2016)

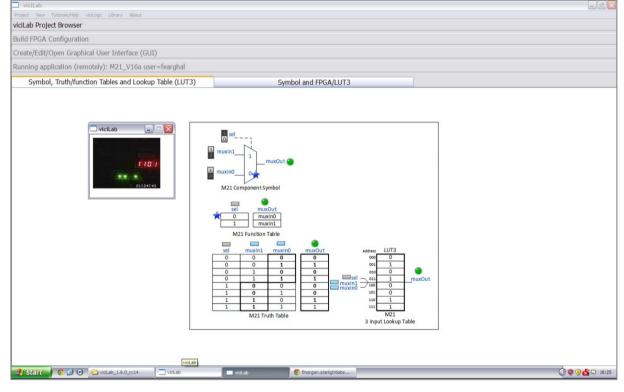

O laboratório *Vicilogic*, ilustrado na Figura 5, possui dois módulos, o *Vicilern*, que conta com um curso online interativo com vídeos e animações, que faz a introdução no aprendizado de sistemas digitais e o módulo *Vicilab*, que conta com uma ferramenta desktop para o sistema operacional Microsoft Windows, onde o usuário tem acesso a um kit de desenvolvimento FPGA real, através da aplicação desktop remotamente, disponível para download no módulo *Vicilab*, a Figura 6 ilustra a ferramenta desktop *viciLab*, onde é possível ver uma janela sobreposta com a visualização por vídeo do kit de desenvolvimento FPGA e no centro da tela os controles, que possibilitam controlar o FPGA remotamente.

Figura 6 – Aplicação desktop *viciLab* do autor Morgan, F.

Fonte: (Próprio autor, 2016)

Os trabalhos correlatos descritos neste item reforçam a importância de um laboratório e o seu tempo de uso para o desenvolvimento do aprendizado prático, através de laboratórios de acesso remoto.

Do primeiro trabalho do autor Trevelyan, J. (2004), a ideia de um laboratório de orçamento normal ou baixo de operação, foi levado em consideração no desenvolvimento deste projeto, resultando em um laboratório remoto simplificado, de baixo orçamento e de fácil manutenção e acesso.

Do primeiro trabalho, autor Trevelyan, J. (2004), segundo trabalho de J. S. Pastor et al (2004) e o terceiro trabalho dos autores Hashemian, R. e Riddley, J. (2007), descrito neste capítulo, reforçam a eficácia da utilização do laboratório de acesso remoto e os seus resultados para o aprendizado prático.

O quarto trabalho do autor Morgan, F. (2011), apresentado neste item, é o mais similar a este projeto, que também abordou o laboratório de acesso remoto baseado em um website, porém a visualização, controle e envio de projetos é feito através de uma aplicação desktop para o sistema operacional Windows, sendo neste ponto o maior diferencial deste projeto, no qual a visualização, controle e envio é feito diretamente no website do projeto desenvolvido, conforme descritos no item 3.1 e os seus sub itens, sem a necessidade de baixar qualquer *software* adicional e independente do sistema operacional utilizado o tornando mais acessível e simples de utilizar.

#### 3. Arquitetura

Este capítulo aborda a estrutura e a arquitetura do projeto e como funciona os componentes e módulos do Laboratório Remoto e as suas comunicações.

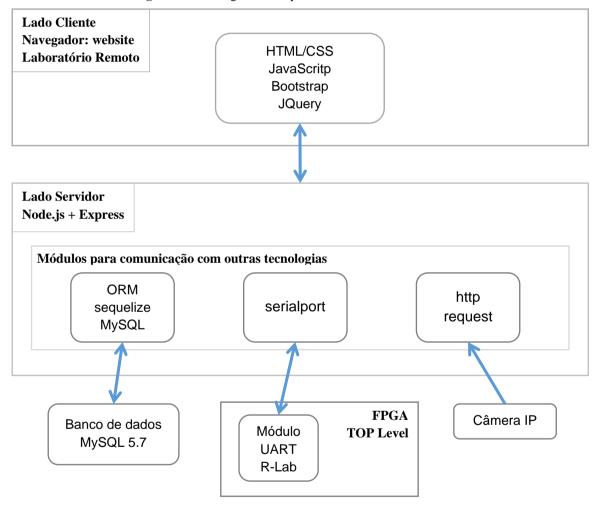

O Laboratório Remoto, como citado anteriormente na introdução, é uma plataforma web desenvolvido no modelo de cliente servidor, a Figura 7 ilustra uma visão geral da arquitetura do Laboratório Remoto.

Figura 7 – Visão geral da arquitetura do Laboratório Remoto.

Fonte: (Próprio autor, 2016)

#### 3.1. Estrutura do lado cliente.

As interfaces do lado cliente do Laboratório Remoto foram desenvolvidas utilizando HTML5/CSS, Bootstrap e JQuery, como citado no item 1.7.5. O *framework* Bootstrap de CSS, provê o visual das interfaces através da utilização de suas classes CSS e animações através da biblioteca JQuery, o *framework* possui visual limpo leve e simples que torna a navegação agradável aos usuários. Para a manipulação dos elementos do lado cliente das interfaces não foi utilizado nenhum *framework*, sendo utilizado apenas JavaScript puro.

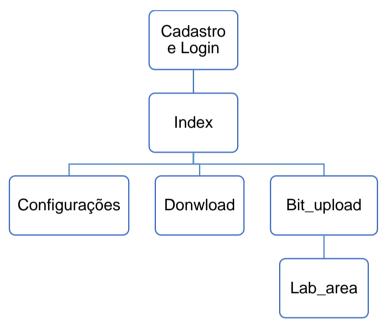

Figura 8 - Mapa das view/interfaces lado cliente.

Fonte: (Próprio autor, 2016).

Na Figura 8 é apresentado a estrutura das interfaces de usuário, a interface do Laboratório Remoto é composta basicamente por 6 tela ou *views*, que são descritos a seguir.

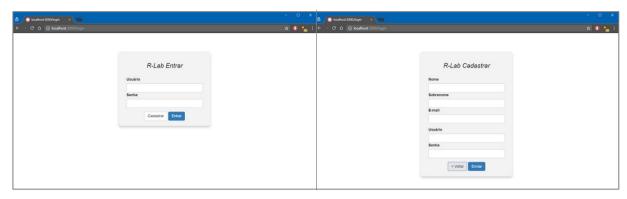

#### 3.1.1. Tela de cadastro e login

Tela inicial, onde o usuário faz o seu cadastro ou login caso já tenha cadastro, o usuário sempre é redirecionado para esta tela caso não tenha efetuado login. A Figura 9, mostra uma visualização da *view* de login e cadastro, ambos login e cadastro fazem parte da mesma *view*, são alternados pelo JavaScript no lado cliente.

Figura 9 – Tela de Login e cadastro.

Fonte: (Próprio autor, 2016).

#### 3.1.2. Tela inicial index

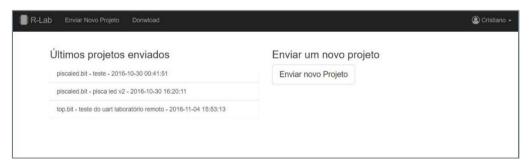

Página inicial do laboratório (Figura 10) esta página dá acesso aos outros recursos do laboratório, Configuração, Download e a tela de upload do arquivo bit, nesta tela o usuário tem a visualização dos últimos projetos, arquivos \*.bit, enviados com sucesso, é possível utiliza-lo novamente caso queira repetir a simulação do mesmo.

Figura 10 – Tela inicial do laboratório.

Fonte: (Próprio autor, 2016)

#### 3.1.3. Tela de configurações:

Esta interface é onde é feito a configuração dos kits de desenvolvimento FPGAs conectados ao servido, esta configuração só é necessária ser executada apenas uma vez, ou sempre que for adicionado um novo kit de desenvolvimento ao servidor, esta tela pode ser acessível a partir do menu com o nome de usuário caso este seja administrado, no canto superior

direito da barra de navegação conforme mostra a Figura 11. Nesta tela é listado os nomes/modelo dos FPGAs detectados pelo servidor e todas as postar seriais detectadas ativas com algum dispositivo conectado.

Na Figura 11 é ilustrado que um dispositivo foi detectado no servido, para a configuração basta selecionar uma porta para o dispositivo, esta porta é a utilizada para controlar o projeto desenvolvido para o FPGA, através da porta UART, como ela não é detectada automaticamente, é necessário saber qual a porta correta para associar ao Kit do FPGA, é obrigatório associar ao menos uma porta a um kit de desenvolvimento FPGA para prosseguir com a configuração.

No último campo é possível adicionar o link ou IP da câmera IP que é carregado quando a simulação estiver em execução, este não é um item obrigatório, caso não adicionado a simulação funciona normalmente, porém sem visualização, este item pode ser adicionado posteriormente voltando ao menu de configurações.

Configurações do dispositivo.

Associe cada dispositivo a uma porta diferente.

FPGA

Porta

Camera IP (URL direta do video)

1 - xc6six16

Configura

Configura

Sair

Configura

Configura

Configura

Sair

Comman

Comman

Comman

Comman

Configura

Comman

Comman

Configura

Sair

Configura

Comman

Comman

Comman

Configura

Sair

Figura 11 – Tela de configurações

Fonte: (Próprio autor, 2016).

#### 3.1.4. Tela download

Nesta tela, Figura 12, está disponível para download o módulo VHDL UART R-Lab e um exemplo de utilização, este módulo é o responsável pela comunicação entre o FPGA e o servidor, este módulo é implementado no lado do FPGA, para o usuário utilizar no seu projeto, caso o usuário do laboratório opte por não utilizar este módulo, ele pode enviar normalmente seu arquivo bit este é programado no kit do FPGA do servidor, mas não é possível controla-lo, tendo apenas a visualização. Fica disponível para download também nesta página os últimos 10 arquivos bit que o usuário enviou com sucesso para o servidor.

Figura 12 – Tela de downloads.

Fonte: (Próprio autor, 2016).

# 3.1.5. Tela bit\_upload:

Esta é a interface onde o usuário efetua o upload do arquivo .bit, que é gerado pelo sintetizador da Xilinx a ferramenta ISE Design Suite, descrito no item 1.3.2. Tem um campo/botão para selecionar o arquivo em disco, um campo para selecionar o modelo do FPGA disponível e um campo de descrição opcional, após o envio caso nenhum erro ocorra o usuário é redirecionado diretamente para a tela Lab\_area onde ele pode visualizar e controlar o FPGA.

Selecione o arquivo .bit

Selecione o dispositivo

Descrição

Opcional

IMPACT debug:

INFO;IMPACT;591 - '1': Added Device xc3550e successfully.

INFO;IMPACT;583 - '1': The idcode read from the device does not match the idcode

in the badl File.

INFO:IMPACT;1576 - '1': Device IDCODE: 0000000010000010010011

INFO:IMPACT;1579 - '1': Expected IDCODE: 0000000010000010010011

Figura 13 - Tela de upload do arquivo bit

Fonte: (Próprio autor, 2016).

A Figura 13 ilustra a tela Bit upload com uma mensagem de erro do iMPACT, onde foi feita a tentativa de envio de um arquivo bit gerado para um modelo de FPGA diferente do disponível no kit ligado ao servidor, neste caso o usuário não é redirecionado. O funcionamento no lado servidor é descrito no item 3.2.5.

## 3.1.6. Tela de simulação, controle e visualização, lab\_area

A tela lab\_area é a tela onde pode ser visualizado o resultado do projeto que foi enviado, em execução, caso o projeto contenha o módulo fornecido na tela de download para fazer a comunicação com o servidor, é possível controlar a aplicação em execução da forma em que o usuário projetou os comandos recebidos pelo módulo UART. A Figura 14 ilustra o exemplo de teste que é distribuído junto do módulo UART R-Lab em execução.

R-Lab Enviar Novo Projeto Cristiano ■ Video O E/S Rx/Tx Entrada Tx: O Switches ASCII: 3 - HEX: 33 - Binário: 01010001 ASCII: 1 - HEX: 31 - Binário: 01001001 Switch 01 ASCII: 2 - HEX: 32 - Binário: 01010000 Switch 02 ASCII: 7 - HEX: 37 - Binário: 01010101 Switch 03 Switch 04 Switch 05 Switch 06 Switch 07 Switch 08 Saida Rx: Switch 09 Switch 10 Switch 11 Switch 12 Switch 13 Switch 14 Switch 15 Switch 16

**Figura 14** – Tela de simulação, controle e visualização do Kit FPGA.

Fonte: (Próprio autor, 2016).

No exemplo de teste, os 8 LEDs da parte inferior do kit de desenvolvimento estão ligados nos 8 primeiros *switchs*/chaves, as chaves foram ativadas e os LEDs correspondentes da direita para esquerda foram ligados e no painel de E/S à direita, mostra a entrada que veio do transmissor do módulo UART, no exemplo executado em seu *TOP level*, está implementado

soma + 1 para entrada recebido e envia de volta, foram enviados os números "2", "0", "1" e "6", a caixa de texto "Entrada Tx:" mostra o resultado recebido de volta do FPGA em 3 formas, ASCII, Hexadecimal e binário e o resultado em ASCII pode-se notar que está na sequencia os dígitos "3", "1", "2" e "7", todos incrementados em + 1 como implementado no *TOP level* de teste.

## 3.2. Arquitetura do lado servidor.

O servidor é a parte principal do laboratório, onde está concentrado toda a aplicação e é por onde tramita todas as comunicações do cliente, kit de desenvolvimento FPGA, banco de dados e câmeras, o servidor do Laboratório Remoto foi desenvolvido utilizando como base principal o Node.js com o framework Express.js, descritos nos itens, 1.7.1 e 1.7.3.

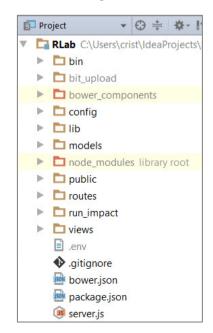

Este tópico aborda a estrutura do servidor e seus módulos, a Figura 15 ilustra a estrutura completa de diretórios do servidor, parte dessa estrutura é gerado pelo *framework* Express descrito no item 3.2.2, os diretórios *config* e *models* fazem parte o ORM Sequelize, descritos no item 3.2.3, *bower\_components* e *node\_modules* são os diretórios das bibliotecas utilizadas no projeto e são descritos no item 3.2.1, o diretório *lib* contém bibliotecas adicionais desenvolvidas para o projeto, item 3.2.4 e por fim *bit\_upload* e *run\_impact* fazem parte do gerenciamento do arquivo .bit enviado pelo usuário do laboratório no item 3.2.5.

Figura 15 – Estrutura completa de diretórios do servidor.

Fonte: (Próprio autor, 2016).

## 3.2.1. Dependências

Este projeto utiliza dois gerenciadores de pacotes de dependência, o NPM que é o gerenciador de dependências do Node.js e o Bower, que é um gerenciador de pacotes para web lado cliente.

Para facilitar no desenvolvimento, *deploy*, distribuição e gerenciamento bibliotecas de uma aplicação, utiliza-se os gerenciadores de pacotes, eles são responsáveis por instalar todas as dependências nas versões descritas pelo desenvolvedor, necessárias para o correto funcionamento da aplicação.

Ainda na Figura 15, nota-se os arquivos JSON no diretório raiz do servidor, *bower.json* e *package.json*, estes são arquivos que contém as informações das dependências do laboratório.

A Figura 16 mostra o conteúdo de cada um dos arquivos JSON, ambos possuem o atributo "dependencies", onde estão listadas todas as dependências do Laboratório Remoto, seguidas de suas referentes versões na frente do nome, no *bower.json*, estão as dependências utilizadas no lado cliente, que são armazenadas no diretório "*bower\_components*" Figura 15 e são servidor como os arquivos estáticos, igual ao diretório "*public*", descrito no item 3.2.2.

Figura 16 – Arquivos de dependências package.json e bower.json

```

package.json

bower.json

{

"name": "RLab",

"description": "Laboratório re...",

"name": "RLab",

"description": "Laboratorio R...",

"version": "0.9.0",

"main": ""

"private": true,

"authors": [

"scripts": {

"start": "node ./bin/www"

"Vicente, C. <cristiano@live.jp>"

],

"license": "MIT",

"homepage": "",

"dependencies": {

"bcryptjs": "^2.3.0",

"private": true,

"body-parser": "~1.15.1"

"ignore": [

**/.*",

"cookie-parser": "~1.4.3",

"debug": "~2.2.0"

"node modules",

"dotenv": "^2.0.0"

"bower_components",

"express": "~4.13.4"

"test",

"tests"

"fs-extra": "latest",

"hbs": "~4.0.0",

"jsonwebtoken": "^7.1.9",

'dependencies": {

"bootstrap": "^3.3.7",

"morgan": "~1.7.0",

"multer": "^1.2.0",

"font-awesome": "^4.6.3"

"mysql": "^2.11.1"

"request": "^2.78.0"

"sequelize": "^3.24.3"

"serialport": "^4.0.3",

"serve-favicon": "~2.3.0"

}

```

Fonte: (Elaborado pelo Autor, 2016).

As dependências listadas no "package.json", são armazenadas no diretório "node\_modules", este contém todas as dependências que funcionam no lado servidor incluindo as dependências de dependências, de forma compartilhada, caso uma biblioteca dependa de outra, se sua dependência já existir apenas um código é armazenado e compartilhado entre as bibliotecas (NPM, 2016).

Segue uma breve descrição do que são as dependências listadas na Figura 16;

- **bcryptjs:** biblioteca de criptografia, utilizada para codificar a senha de usuário armazenado no banco de dados, para segurança e maior privacidade de senha.

- **body-parser:** dependência padrão do *framework* Express, serve para fazer o análise do corpo das requisições e adicionas as informações analisadas no *req.body*.

- cookie-parser: outra dependência padrão do Express, serve para fazer o análise do atributo Cookie do cabeçalho de requisição HTTP e adiciona as informações no req.cookies.

- debug: módulo utilizado pelo Express para registrar as correspondências de rodas e seus ciclos de requisição e resposta e também dos outros módulos que estão em uso. (EXPRESS, *Debugging Express*, 2016).

- **dotenv:** Este módulo carrega as informações do arquivo **.env**, que são variáveis de ambiente, do tipo porta http a ser utilizado, modo de execução, e.g. *production* ou *development*, o arquivo .env está presente no diretório raiz do servidor Figura 15.

- **express:** *framework* Express, descrito nos itens 1.7.3 e 3.2.2.

- **fs-extra:** Esta dependência complementa algumas funções na biblioteca padrão fs, *file system*, como a função copiar arquivo, ausente na biblioteca padrão, responsável por acessar e manipular arquivos do sistema.

- **hbs:** Módulo responsável por renderizar *views* html no lado servidor.

- **jsonwebsoken:** Módulo que gera e valida os *tokens* de acesso, utilizado pelo módulo *authentication*, descrito no item 3.2.4.

- morgan: Módulo padrão do Express, que registra as requisições http.

- **multer:** Módulo para manipulação de requisições do tipo *multipart/form-data*, são requisições utilizadas principalmente para upload de arquivos.

- mysql: Drive do banco de dados MySQL para o Node.js, utilizado pelo ORM Sequelize para realizar a conexão com o banco de dados.

- **request:** Módulo que faz requisições http, utilizado neste projeto para requisitar a url ou IP da Câmera IP, descrito no item 3.4.

- **sequelize:** ORM Sequelize, descrito no item 3.2.3.

- **serialport:** Módulo para acessar portas seriais para leitura e escrita.

- serve-favico: Módulo padrão do Express, apesar de opcional, ele vem junto das dependências do Express, ele serve o ícone para a página web que aparece na aba do navegador.

- **bootstrap:** Framework CSS que provê o visual das view, descrito nos itens 1.7.5 e 3.1.

- **font-awesome:** Framework CSS de ícones em forma de fonte.

A referência e documentação de todos os módulos descritos neste item podem ser encontradas no site do gerenciador de pacotes do Node.js NPM <a href="https://www.npmjs.com/">https://www.npmjs.com/</a>>.

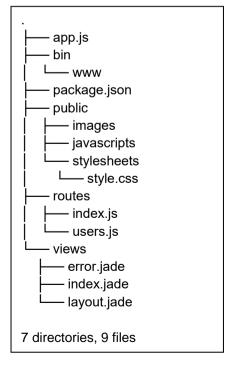

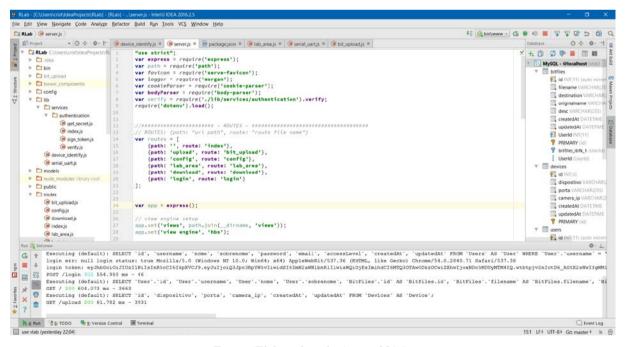

### 3.2.2. Estrutura do express.js

A estrutura base de diretórios do servidor é gerado pelo *framework* Express.js, que conta com os pacotes/módulos necessários para prover recursos de uma aplicação web. A Figura 17 ilustra a estrutura gerada pelo express-generator, ferramenta do *framework* express.js. (EXPRESS, 2016).

**Figura 17** – Estrutura de diretórios base gerado pelo express-generator.

Fonte: (EXPRESS, 2016).

A estrutura gerada pelo express-generator, Figura 17, contém 7 diretórios base e 9 arquivos, sendo os principais descritos a seguir;

- **app.js:** Contém todas as configurações iniciais do servidor, como declarações de rotas e extensões utilizadas. O app.js neste projeto foi renomeado para server,js.

- www: É o script de inicialização do servidor, pode ser visto descrito no package.json na Figura 16 no atributo "scripts: start", ele importa o app.js que carrega todas as configurações do servidor, o www é executado/interpretado pelo processo node.exe.

- **package.json:** Este é o arquivo json do gerenciador de pacotes NPM do Node.js, visto na Figura 16, qual contem meta-dados referentes ao projeto, como descrição, dependências e configurações, (NODEJITSU, *What is the file `package.json`?*, 2016).

- public: Diretório contém os arquivos estáticos do lado cliente da aplicação web, como

JavaScript, imagens e CSS.

- routes: Neste diretório ficam os códigos responsáveis por gerenciar os recursos servidos de cada rota da aplicação web, quando uma rota é chamada e.g. http://dominio.com/users a rota users.js é requisitado no servidor, está trata a requisição e responde com um recurso, que pode ser texto simples, html ou arquivos.

- **views:** Contém as views, interfaces a serem servidas para o cliente, podem ser em html, ou html pré renderizado no lado servidor, o express-generator conta com 7 opções (ejs, hbs, hjs, jade, pug, twig, vash), de motores de renderização html para o lado servidor, (EXPRESS, 2016).

### 3.2.3. ORM Sequelize, models e banco de dados

O framework Express não conta com um gerenciador de bando de dados ou ORM, sendo necessário criar classes para comunicação com o banco de dados ou utilizar módulo que faça as comunicações com o bando. Este projeto utiliza o Sequelize, um ORM para o Node.js que suporta os bancos de dados PostgreSQL, MySQL, MariaDB, SQLite e MSSQL (SEQUELIZE, 2016).

Ilustrado na Figura 18, estão 2 diretórios do ORM Sequelize, o item **config/config.json** possui as informações de conexão com o banco de dados, como "username", "password", "database", "host" e "dialect", dispostas em 3 objetos "development", "test" e "production",

permitindo utilizar 3 diferentes configurações para cada ambiente, de desenvolvimento, teste e produção.

Ainda na Figura 18, há o diretório das **models**, este possui as classes referentes as tabelas do banco de dados, neste diretório há 3 classes, sendo elas "user.js", "bit\_file.js" e "device.js", o arquivo "index.js" não é uma *model*, dentro da estrutura de módulos do Node.js, é possível importar outras classes, e.g. utilizando o método require('./../models/user');, está importando a classe *user.js* do diretório *models*, porém pode-se importar o diretório todo como um pacote de classes caso este tenha um *index.js* referenciando seu conteúdo, e.g. require('./../models');, está requisição importar todas as classes do diretório *models* que estão especificadas no *index.js*.

config

config.json

models

bit\_file.js

device.js

index.js

user.js

Figura 18 – Diretórios do ORM Sequelize.

Fonte: (Próprio autor, 2016).

O ORM Sequelize possui um método "sequelize.sync()", para sincronização das models no banco de dados, ele cria as tabelas do banco de dados, no esquema especificado no arquivo de configurações **config/config.json**, atributo "database", conforme modelado nas classes do diretório "models", este método possui 1 parâmetro, atributo "force", que pode ser verdadeiro ou falso, quando verdadeiro sempre que executado ele executa um DROP em todas as tabelas do esquema configurado e as recria novamente, utilizado no desenvolvimento e na modelagem inicial das models para fins de teste, quando configurado para falso, o método "sequelize.sync()", apenas verifica a existência das tabelas, se as mesmas não existirem ele as cria, este último assim utilizado para *deploy* da aplicação.

Este projeto implementa o método em sua inicialização em modo falso, sendo necessário apenas criar o esquema no banco de dados e configurar o arquivo **config/config.json**. Na Figura 19 é ilustrado o esquema do banco de dados gerado pelo Sequelize.

Visualisation for MySQL - @localhost users devices e id e id username varchar(21) dispositivo varchar(255) nome varchar(50) porta varchar(255) camera ip sobrenome varchar(50) varchar(255) password varchar(70) createdAt email varchar(70) updatedAt datetime accessLevel createdAt datetime updatedAt datetime bitfiles ? id filename varchar(255) destination varchar(255) originalname varchar(255) desc varchar(255) created∆t updatedAt **UserId** int(11)

Figura 19 - Modelo do banco de dados.

Fonte: (Elaborado pelo Autor, 2016).

Nas classes de modelo do Sequelize é possível descrever não somente os atributos da entidade, mas também suas relações, as chaves, indexes, tipos de dado e métodos. Tomando como exemplo a Figura 19, mostra a tabela *users* e *bitfiles* relacionadas, na *model* da classe *user* é declarado esta relação e.g. "User.hasMany(models.BitFile);" e na model *bitfile* e.g. "BitFile.belongsTo(models.User);".

O ORM possui um conjunto completo de métodos para *querying* para todas as principais sintaxes SQL, permitindo executar todas as chamadas ao bando através de métodos das classes sem a necessidade projetar as *strings* SQL, e.g. "User.findAll()", busca todos os usuários, "User.create();", insere um novo usuário. Conforme descrito na documentação do Sequelize. (SEQUELIZE, 2016).

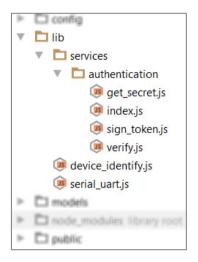

### 3.2.4. Bibliotecas desenvolvidas para o projeto

Para o projeto do Laboratório Remoto foram desenvolvidos três módulos complementares, que são, "authentication", "device\_identify" e "serial\_uart", destacados na Figura 20 no diretório "lib", o módulo authentication foi desenvolvido para fazer a autenticação

do login do usuário no laboratório e controlar sua seção, pois o *framework* Express não conta com um módulo para autenticação.

Os seus métodos estão divididos em arquivos separados no diretório *authentication* e são relacionados pelos arquivos *index.js*, bastando importar o diretório para ter todos os métodos como fora descrito no item 3.2.3, a forma de importar todas classes do diretório *models*, o módulo de autenticação gera um *token* que é adicionado no *cookie* do navegador, para verificar e identificar o usuário e a seção em todas as requisições, permitindo fazer o controle de acesso as rotas.

O módulo "device\_identify", faz a identificação do modelo do FPGA do kit de desenvolvimento e das portas seriais ativas no sistema, o kit de desenvolvimento é conectado ao servidor utilizando duas portas USB, como fora descrito no item 1.4.2, na Figura 3 destacado por dois retângulos numerados, estão as duas portas USB do kit utilizado no desenvolvimento deste projeto.

A porta com nome Adept USB é identificada utilizando a ferramenta iMPACT em modo batch, "linha de comando", o módulo "device\_identify", utiliza o método execFile() da biblioteca nativa do Node.js "child\_process", que permite o servidor executar um processo filho de um arquivo executável (NODE.JS, Child Process, 2016), assim este módulo pode instanciar um processo do iMPACT, e.g. exec('impact', ['-batch ./run\_impact/identify.cmd']), este comando executa o iMPACT em modo -batch e passa o arquivo identify.cmd, que contém a sequência de comandos para identificar os FPGAs conectados na máquina, a sequência de comandos executado utilizando o identify.cmd são;

- **setmode -bscan**; seleciona o modo de configuração para buscar dispositivos.

- **setCable -p auto**; configura a velocidade e a porta para modo automático.

- identify; identifica cada um dos dispositivos listados pelo bscan.

- info; imprime as informações dos dispositivos, este é retornado em forma de string pelo método em execução.

- quit; encerra a execução do iMPACT. (Xilinx Inc, 2016)

O módulo de identificação faz o parse das informações retornados pelo iMPACT, criando uma lista de dispositivos numerados e com o nome do modelo do FPGA, sendo o número da lista o parâmetro **-p** do comando **setCable** que é utilizado posteriormente para selecionar o FPGA a ser programado. Os dispositivos reconhecidos, são listados na tela de configurações para serem associados a uma porta serial manualmente, pois a ferramenta iMPACT não detecta as portas seriais, estas são detectadas pela biblioteca "SerialPort".

Figura 20 – Bibliotecas desenvolvidas para o projeto.

Fonte: (Elaborado pelo Autor, 2016).

O terceiro módulo destacado na Figura 20, é o "serial\_uart", este módulo possui cinco métodos, sendo um de configuração, um de escrita na porta serial, um de leitura da porta e dois para tratamento de concorrência de acesso ao dispositivo FPGA, o módulo de leitura também utiliza a biblioteca "SerialPort", que é responsável por abrir a conexão serial com a porta UART do kit de desenvolvimento.

Após a configuração de dispositivo e porta, como descrito no item 3.1.3, é chamado o método **serial\_uart.setup\_uart()**; o qual faz uma verificação no banco de dados e carrega as configurações das portas que foram persistidas após a configuração feita no item 3.1.3, abrindo as portas seriais que foram associadas, para cada porta serial aberta é atribuído uma instância global da classe "SerialPort", esta instância possui os métodos para escrita e leitura da porta e também a variável de bloqueio de acesso concorrente ao dispositivo FPGA.

O método *setup\_uart()*, também é executado sempre que o servidor for inicializado, reabrindo as portas que estão nas configurações que foram armazenadas no banco de dados caso estas existam, o método de leitura **serial\_uart.read\_tx\_buffer()**; consome a buffer de entrada de dados enviados pelo FPGA, esta *buffer* é preenchida por um *event emitter*.

Grande parte da API núcleo do Node.js é construída em torno de uma arquitetura idiomática assíncrona orientada a eventos em que certos tipos de objetos (chamados "emitters" ou emissores) que periodicamente emitem eventos nomeados que fazem com que os objetos Funcionais ("listeners") sejam chamados. (Node.js, 2016).

O *listener* que recebe os dados da porta serial, chama uma função nomeada SerialPort.on('data') toda vez que a porta serial instanciada receber algum dado vindo do

FPGA, assim preenchendo uma buffer que é consumida pela rota da *view Lab\_area* chamado por Ajax, preenchendo o campo **Entrada Tx**, visto na Figura 14 e descrito no item 3.1.6.

Do método de escrita do módulo **serial\_uart.writer()**; este faz a escrita na porta serial, ele pode receber como parâmetro, os tipos primários *string*, *number* ou objeto *array* dos mesmos tipos primários e também pode receber *Buffer*, que é uma classe que faz parte da API do Node.js qual permite ler e manipular dados binários, de acordo como a documentação:

Antes da introdução do TypedArray no ECMAScript 2015 (ES6), a linguagem JavaScript não tinha nenhum mecanismo para ler ou manipular fluxos de dados binários. A classe Buffer foi introduzida como parte da API Node.js para tornar possível a interação com fluxos octetos no contexto de coisas como fluxos TCP e operações do sistema de arquivos. Agora que TypedArray foi adicionado no ES6, a classe Buffer implementa a Uint8Array API de uma forma que é mais otimizado e adequado para casos de uso do Node.js. (Node.js, 2016).